ARCHIVE VIEW - This event has already occurred Return to COMPASS main page

COMPASS 2025 - Tokyo, Japan

This Year’s COMPASS Theme is Bringing Tomorrow’s Technology to Life.

FormFactor’s COMPASS test and measurement community event brings together FormFactor customers to discuss the technologies and products shaping our future. This year’s event will feature industry leaders and speakers from FormFactor to share lab and production test insights on advanced packages, high bandwidth memory, low noise testing, silicon photonics and optical test, and other technology trends.

2025年2月12日(水)

場所:鉃鋼エグゼクティブラウンジ&カンファレンスルーム

東京都千代田区丸の内1-8-2 鉄鋼ビルディング南館4階

セミナー開催時間:

11:00~17:10(10:30受付開始)

17:10~19:00 レセプション

参加費用:無料

Agenda

セミナータイトルをクリックすると要旨がご覧になれます

English titles and descriptions are available by expanding each item.

時間や内容は予告なく変更する場合がございます

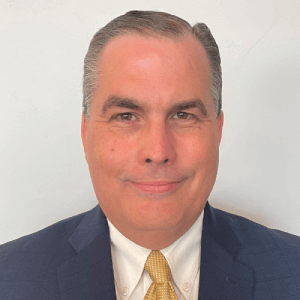

Mike Slessor

President & CEO

FormFactor, Inc.

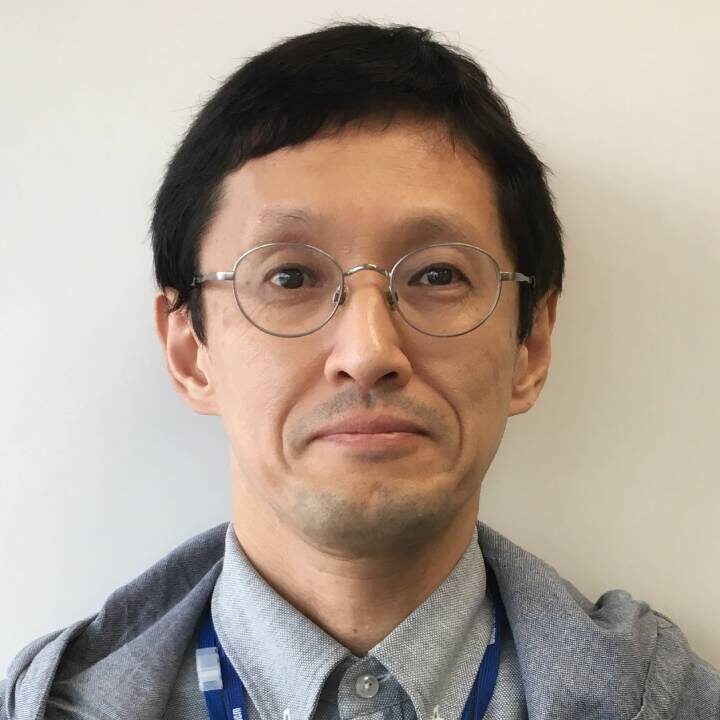

Nobuhiro Kawamata

VP & Country Manager

FormFactor Inc.

代表取締役 川又 信尋

Takashi Kariya

Corporate Vice President / Head of Lab, Device Solutions R&D Japan Advanced Package Lab

Samsung Japan Corporation

Cameron Harker

Sr. Director, Business Development

FormFactor Inc.

Masahiro Sameshima

Senior Staff Application Engineer

FormFactor Japan

Divya Pratap,

Silicon Photonics Program Director

FormFactor Inc.

David Cooke

Sr. Product Marketing Manager

FormFactor, Inc.

Shinji Fujita

Principal/ Test Strategist

Advantest

VP Business Development & Strategic Marketing

Delphon Industries, LLC.

Kevin Tran

Senior Director of Product Marketing

FormFactor Inc.

EXHIBITORS

PRESENTATION REQUEST

Please complete the form below to receive a link to the 2025 presentations

Questions or need help?