# FRT METROLOGY FOR ADVANCED PACKAGING

Kenan Görgülü Head of Sales & Business development - FRT Metrology

### FormFactor FRT Metrology

#### **TECHNOLOGY**

- Leader in Optical Surface Metrology and Inspection

- SurfaceSensh Multi-Sensor Technology

- Various optical point, field of view and film thickness sensors and microscopes integrated in one device

- More than 700 FRT Metrology tools are established worldwide

#### SERVICE

- Global on-site service and maintenance

- Virtual remote support and training

- In-house sensor and software development

- Flexible, expandable and future-proof hardware and software

#### COMPETENCE

- Comprehensive metrology know-how

- More than 25 years of expertise in optical surface measurement

- Highly qualified team of engineers, physicists and experts

- Contract measurements

- ✓ Optical Metrology and Inspection

- ✓ Made in Germany

- √ 700 Tools installed worldwide

- √ 300mm-Tools (40) at major Capex companies in Taiwan, Korea, US

- ✓ Global presence and local support

# FRT: Enabling the ASAP Metrology Roadmap

- FRT is specialized in fully automated multi-sensor metrology system for application-specific advanced packaging (ASAP) measurements

- Cost/Performance optimized for micron-level features

- Supporting the 40μm heterogenous integration HVM

- Leading-customer guided R&D roadmap

- Developing sub-20μm probing technologies

2019-2025 advanced packaging wafer forecast by packaging platforms (12" eq wafer starts per year)

(Source: Status of the Advanced Packaging Industry 2020, Yole Développement, July 2020)

**Applications in Advanced Packaging**

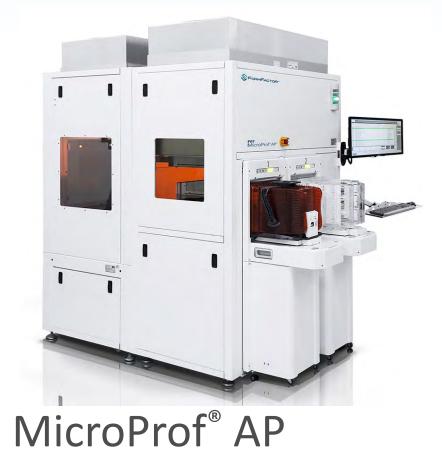

## FRT: Scalable Platform with SurfaceSens<sup>TM</sup>

Standardized<br/>System Platform

MicroProf® 300

MicroProf® MHU

MicroProf® FE

Fully automated

system for Advanced Packaging production

Modular Multisensor Configuration

An example of multi-sensor configuration including topography point sensors, field of view and film thickness sensors

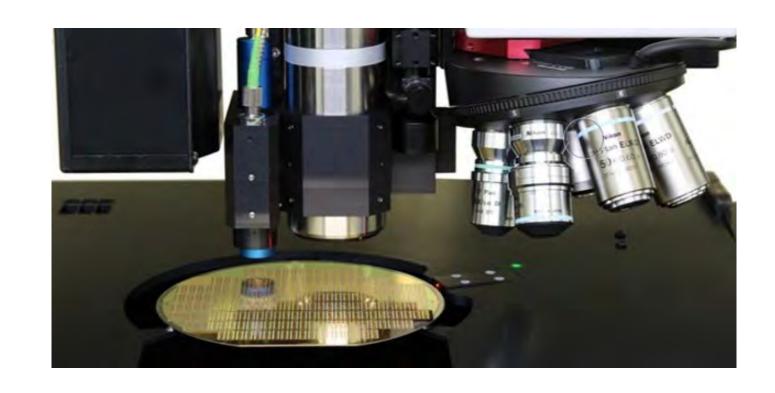

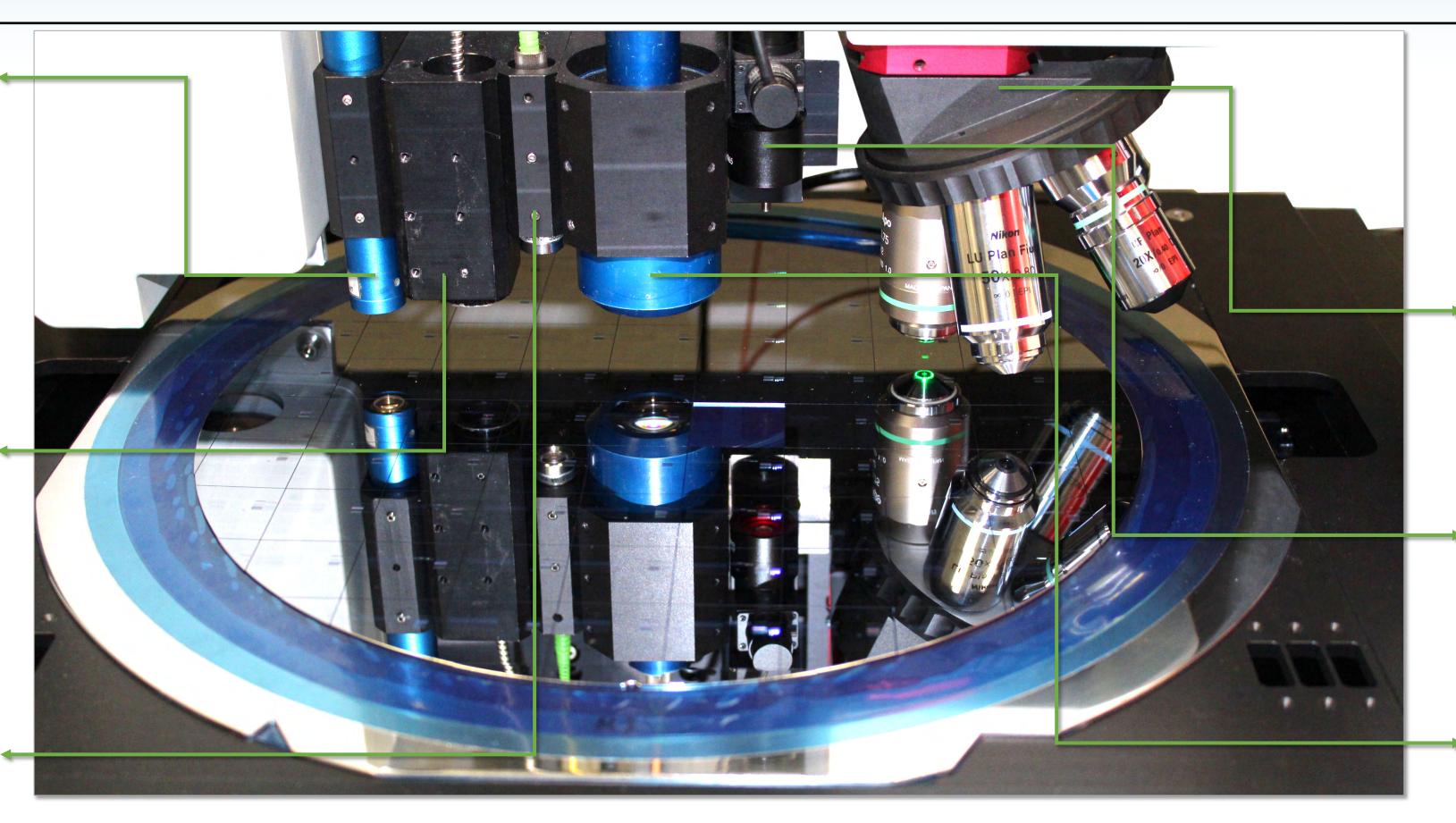

## SurfaceSens<sup>TM</sup>

CWL sensor for surface structure evaluation

FTR Thin Film

Reflectometer for film

thickness analysis

down to 20 nm

IRT Infrared Thickness sensor for wafer thickness measurements

Modular optical metrology set-up for hybrid surface process control

CFM DT confocal microscope / white light interferometer for high resolution

Camera for pattern recognition of alignment structures

CWL sensors in TTV setup (top and bottom sensor)

for TTV, bow, warp evaluation, e.g. up to 3 mm warp

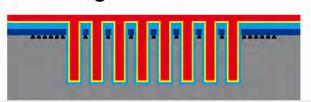

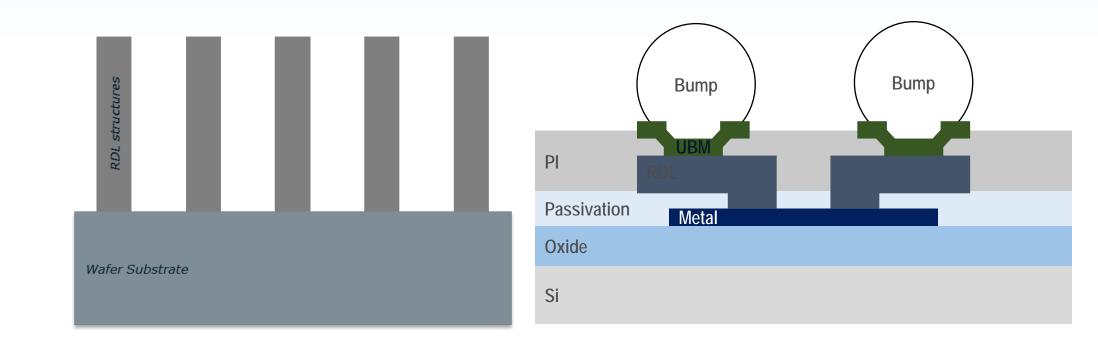

# 2.5D/3D IC Packaging Process Flow

#### Process Flow

#### **FEOL**

## .....

FRT Metrology

Measuring

Applications

**FRT Metrology**

**FRT Metrology**

Measuring

Applications

Measuring

**Applications**

Wafer Topography, Step Height and Width, Thickness and TTV, Roll-Off Amount, Nanotopography, Roughness, Bow, Warpage, Defect Inspection (Particles and Holes)

#### Seed/barrier

Barrier Thickness, Layer Coverage and Uniformity, CD Metrology, Defect Inspection (Layer Cracking, Delamination and Voids)

#### **Patterning**

Photoresist Thickness and TTV, Litho CD, Overlay, Defect Inspection (Particles and Holes)

#### **TSV** filling

Cu Deposition Thickness, CD Metrology, Defect Inspection (Seams, Voids, Dimples, Recesses and Cu-protrusion) Strain around TSVs

#### TSV etching

TSV Etching Depth, Width and Pitch, CD Metrology, Sidewall Angle, Defect Inspection (Photoresist Residuals)

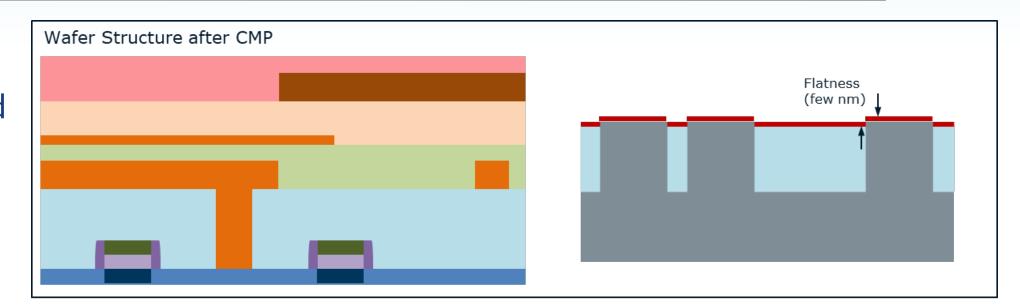

#### CMP

Cu Filled TSVs Topography, Flatness, Uniformity and CD Metrology,

Defect Inspection (Dishings and

Erosions), Wafer Thickness and TTV

#### **TSV** isolation

Dielectric Thickness, Layer Coverage and Uniformity, Defect Inspection (Layer Cracking and Delamination)

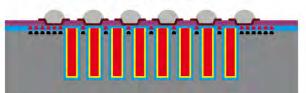

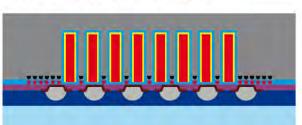

#### RDL/UBM/bumping

Line Metallization Thickness, Width and Roughness; Polymer Thickness, Slope Angle and Stress; RDL Final Package Warpage; UBM Height and Roughness; Solder Bump Height, Width, Pitch, Coplanarity and Defect Inspection

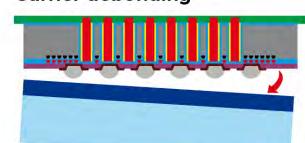

#### Temporary carrier bonding

Carrier/Adhesive Thickness, TTV and Uniformity, Bonded Wafer Thickness, Bow, Warpage and Stress, Alignment Control, Wafer Edge Inspection (Edge Trim), Void Detection

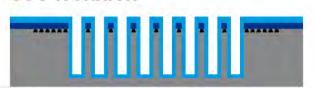

#### **Backside thinning**

Remaining Si Thickness (RST) and Roughness after Grinding, Wafer Edge Inspection (Edge Trim), Defect Inspection (Cracks)

#### Nailing

Remaining Si Thickness (RST) after Etching, Cu Nail Height, Uniformity, Width, Pitch, Coplanarity and Defect Inspection

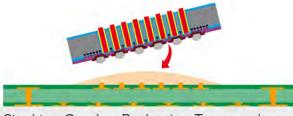

#### Carrier debonding

Solder Bump Height, Width, Pitch,

Coplanarity and Defect Inspection

(Adhesive Residuals, Cracks and

Delamination), Isolation Layer

Thickness and Uniformity

#### Dicing

Protective Film Thickness, Defect

Inspection (Edge Chipping and Cracks)

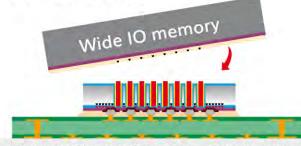

#### Logic to BGA

Stacking Overlay, Packaging Topography, Flatness and Planarity, Thermal Load, Warpage, Deformation, Global and Local Strain

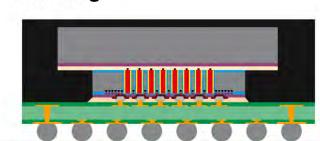

#### C2C stacking

Stacking Overlay, Final Packaging Topography, Flatness and Planarity, Thermal Load, Warpage, Deformation, Global and Local Strain

#### Molding

Mold Topography, Flatness, Roughness and Thickness, Thermal Load, Warpage, Deformation, Global and Local Strain

FRT Metrology

Measuring

Applications

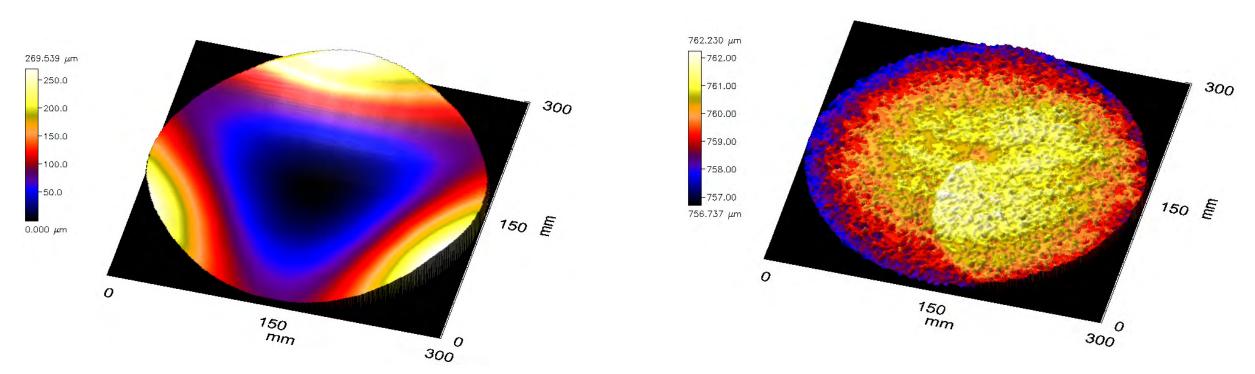

# Wafer Geometry – Thickness, TTV, Bow, Warp

#### Advanced Packaging Challenge:

• Increasing wafer geometry variation for Advanced Packaging, such as thickness variations and warp post-stack, affect later processes and the device quality

#### • FRT Solution:

- High-throughput process control of wafer thickness, TTV, bow and warp using MicroProf® TTV with SEMI compliant sensor setup (top and bottom sensor)

- Determination of global wafer parameters with high throughput

- Evaluation of local wafer parameters

| Warp / μm | Thickness / μm | TTV / μm |

|-----------|----------------|----------|

| 124.47    | 759.92         | 4.71     |

Local wafer parameter map

Wafer top topography (left) and thickness (right), showing dimples

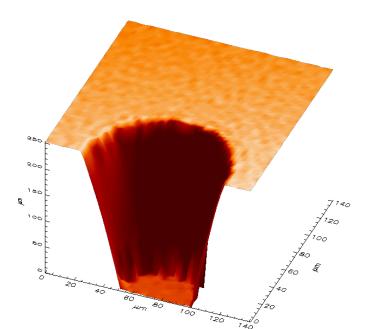

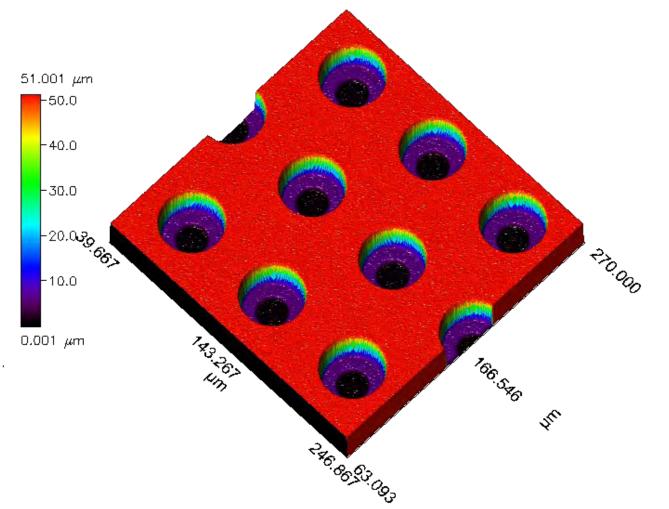

## Etch – Via and Trench Dimensions

- Advanced Packaging Challenge:

- Increasing aspect ratio (AR) for vias and trenches process control

- FRT Solution:

- White light interferometer (WLI) to determine widths and depths

large single via

$\emptyset_{top}$  ~ 100  $\mu m$   $\emptyset_{bottom}$  ~ 60  $\mu m$  t ~ 250  $\mu m$  AR ~ 2.5:1

small via array

$\emptyset \sim 5 \mu m$ , t  $\sim 70 \mu m$ , AR $\sim 15:1$

high AR via

$\emptyset$  ~ 8  $\mu$ m, t ~ 320  $\mu$ m, AR~ 40:1

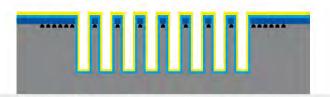

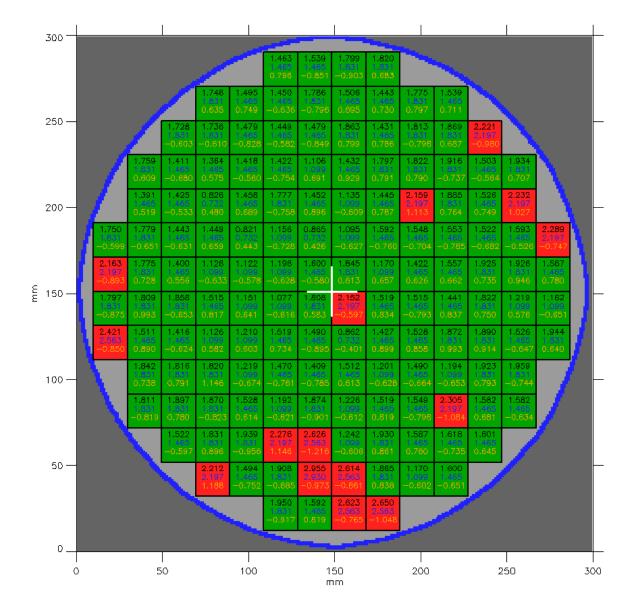

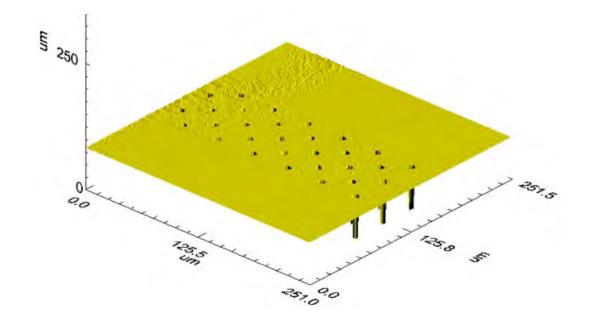

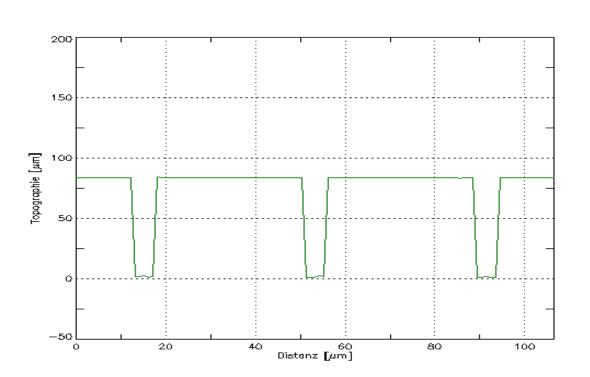

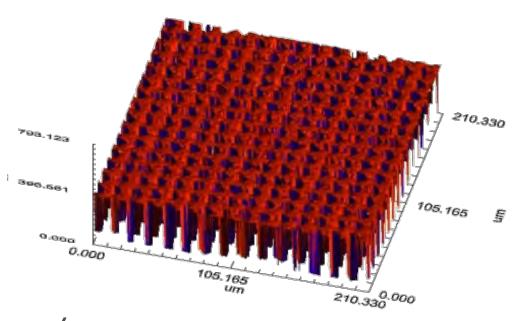

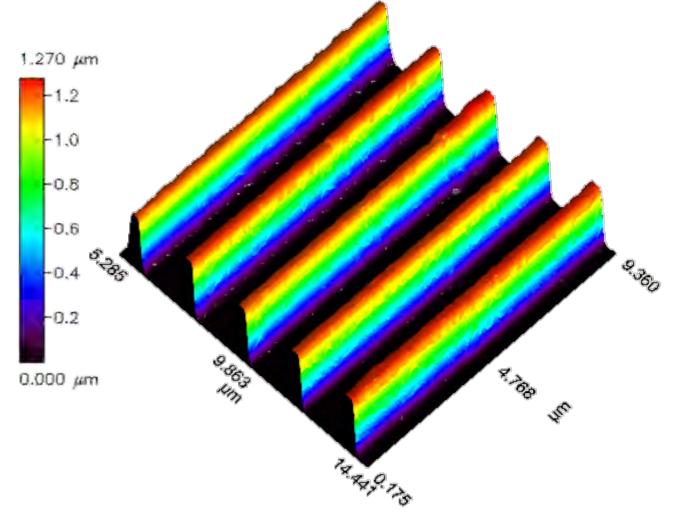

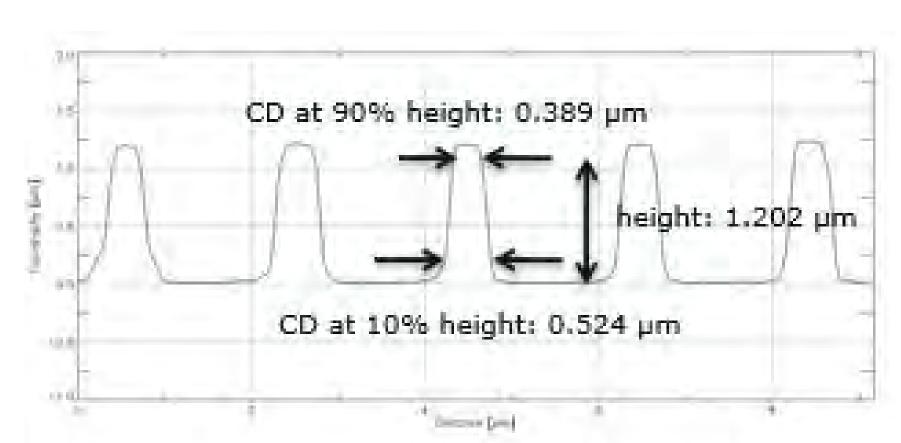

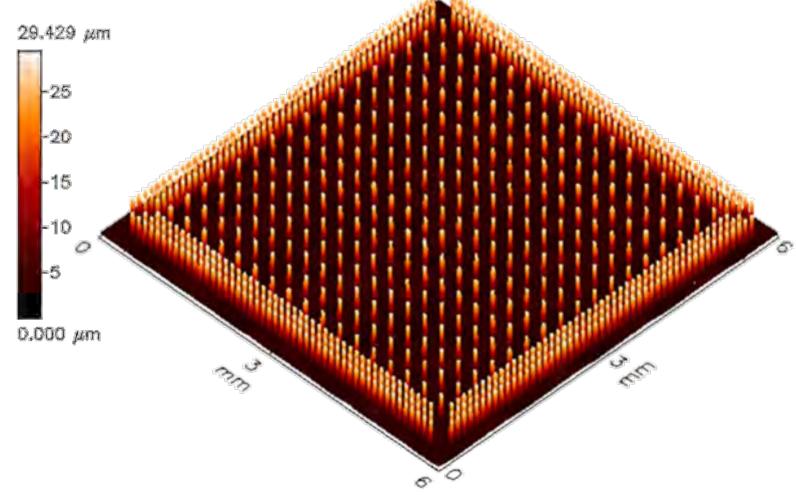

# RDL Width and Height

- Advanced Packaging Challenge:

- High-precision and high-throughput micron-level process control of RDLs

- FRT Solution:

- Evaluation of RDL height and width using WLI with optimized setup for high resolution

- Repeatability of RDL width  $< 0.01 \, \mu m$

- Monitoring of bump heights, widths, pitch and coplanarity according to JESD22-B108

Topography map of RDL structures

RDL topography profile

Bump measurement of full die

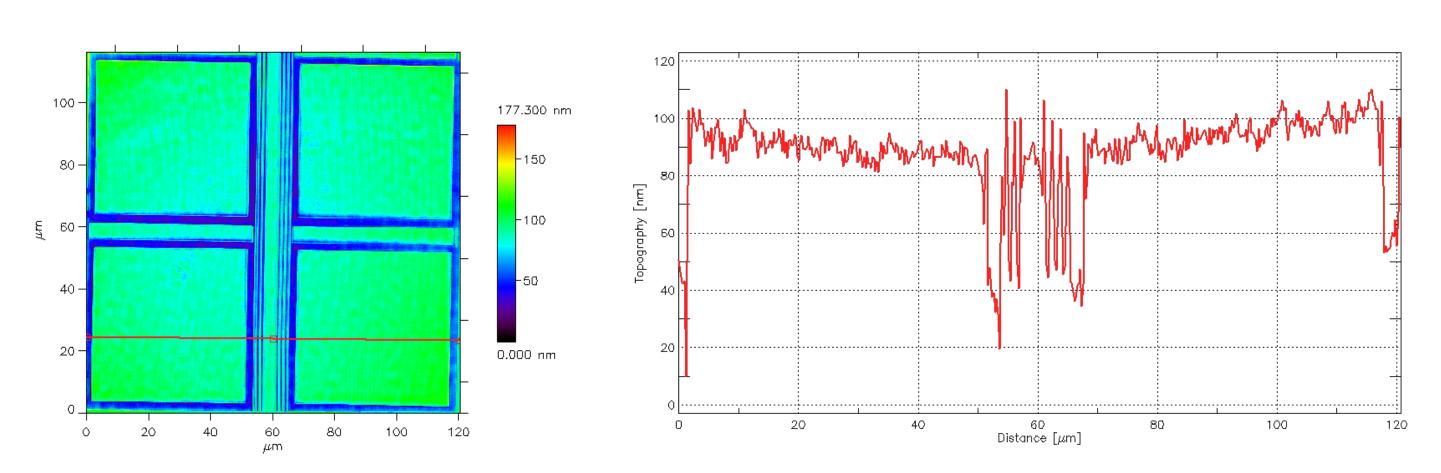

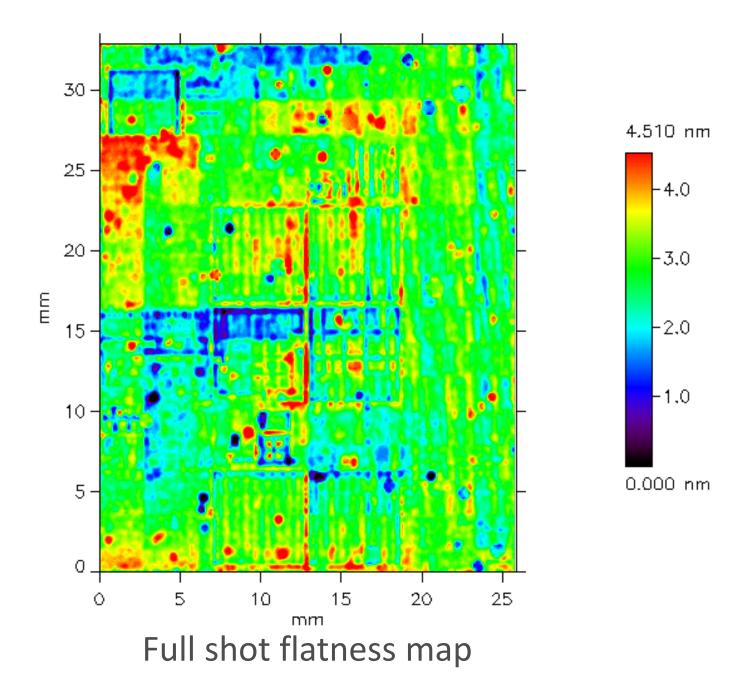

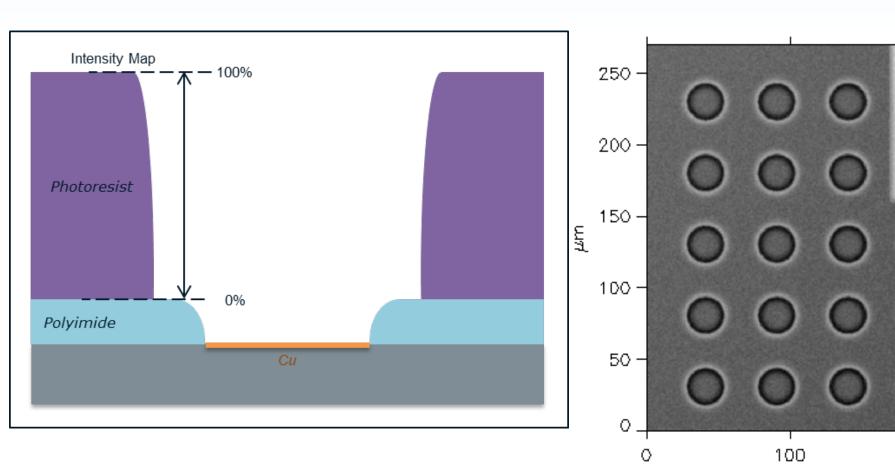

## CMP Die and Wafer Flatness

#### Advanced Packaging Challenge:

• Detrimental surface irregularities post-CMP with increasing number of layers and process steps, resulting in electrical defects of chips and reduced wafer yield

#### • FRT Solution:

- New capability to evaluate die areas up to 25 mm x 35 mm per full shot

- Z-resolution of 0.1 nm

- Measurement time ~0.5 h per full shot, with roadmap to higher throughput for HVM

- Image stitching and big data processing

High resolution mapping (left) and profile (right) of single pad flatness

intensity map

300

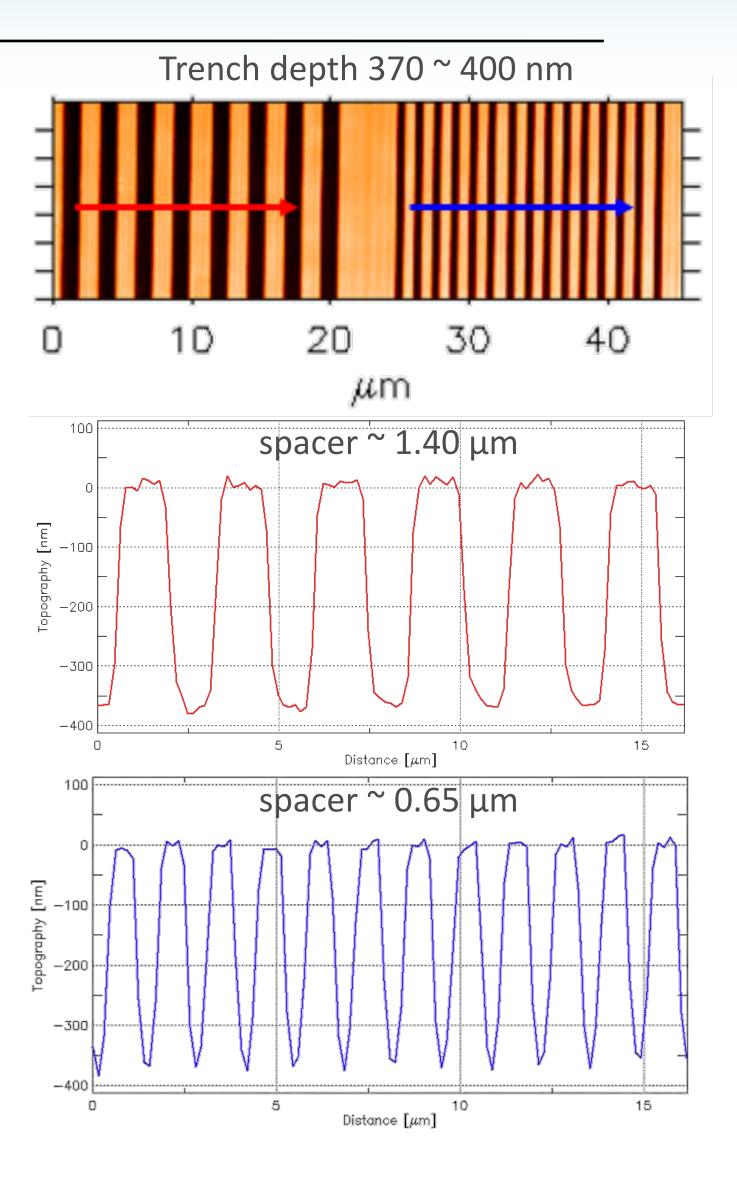

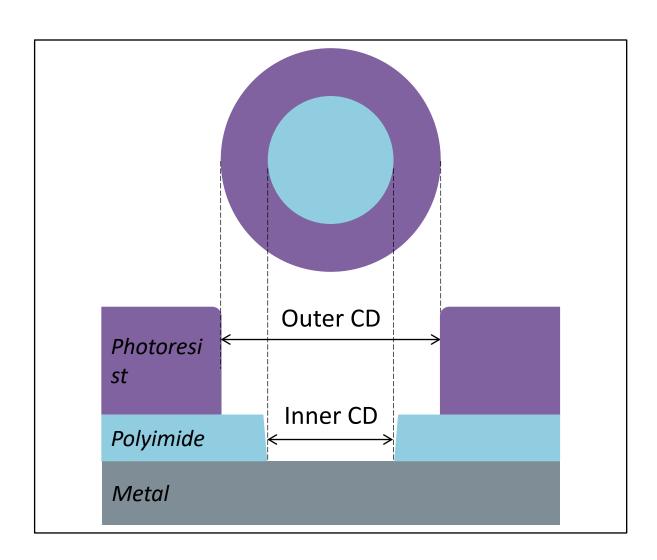

# Critical Dimension and Overlay

- Advanced Packaging Challenge:

- Low CoO monitoring of micro-level CD and overlay

- FRT Solution:

- Measurement with confocal microscope (CFM DT)

- CD and OVL analysis

CD and overlay measurement with CFM

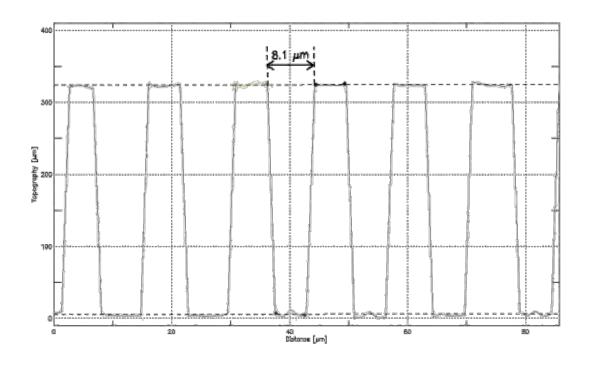

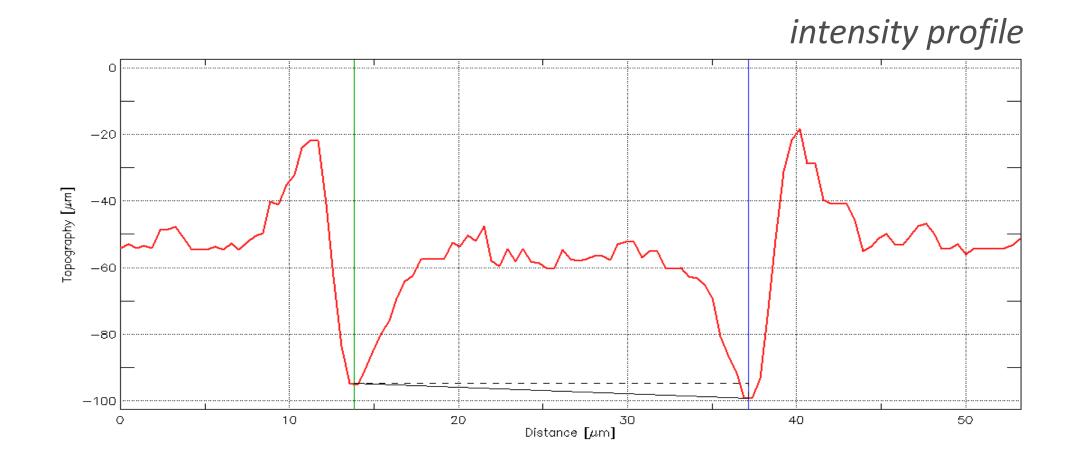

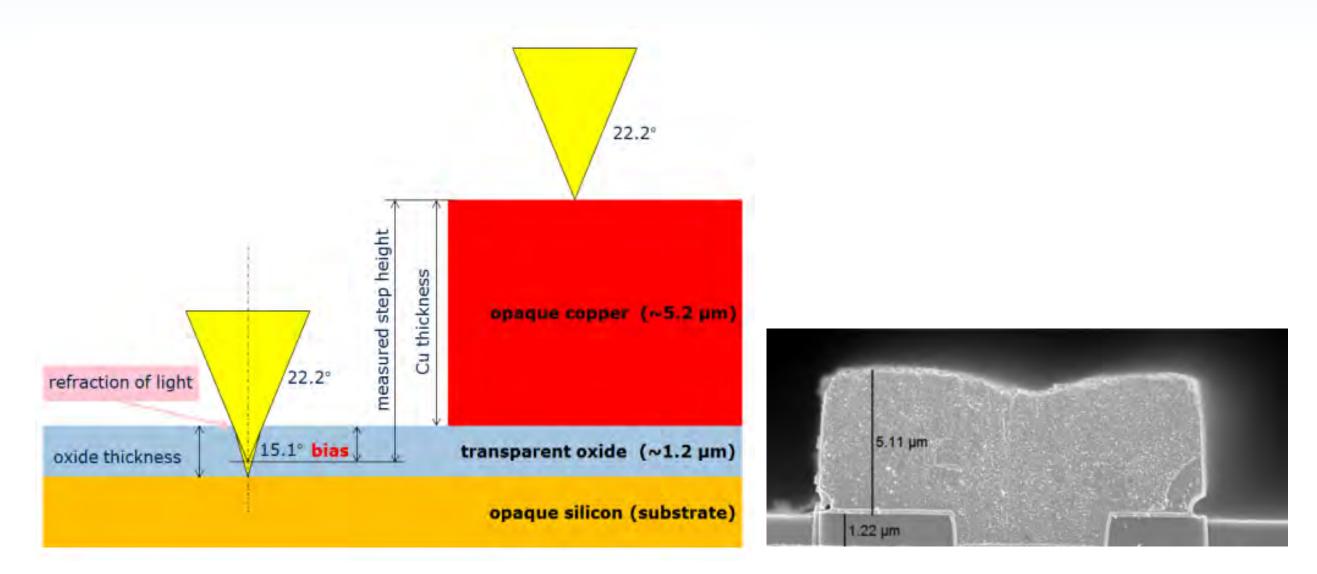

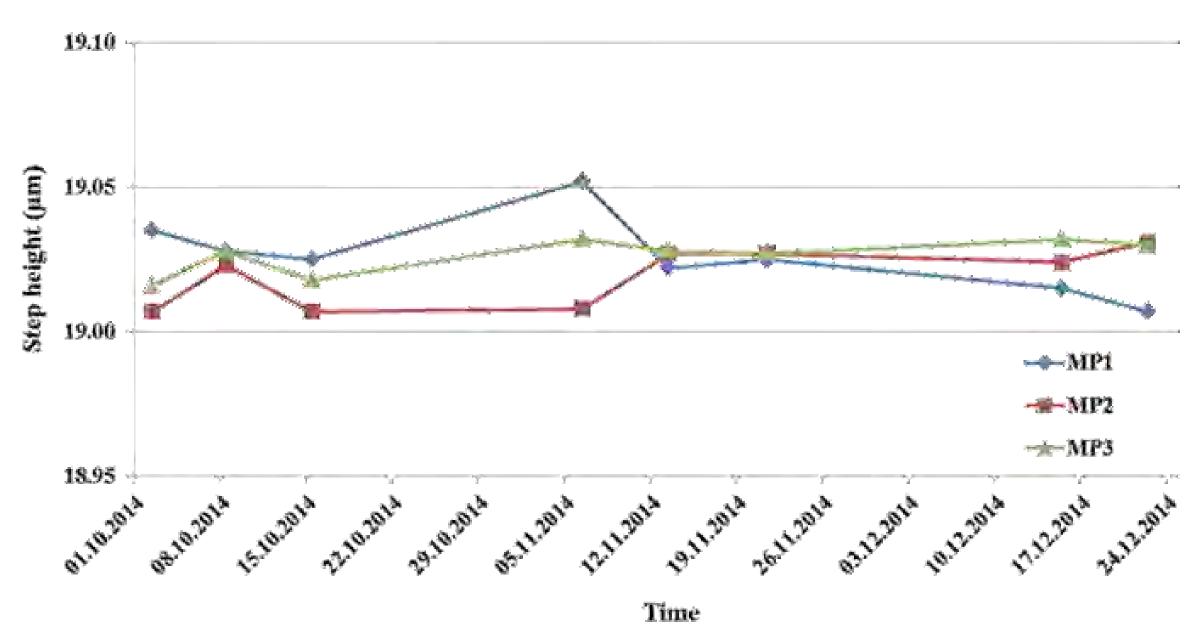

## Production Case Study: Repeatability of Step Height/Width

#### Determination with Hybrid Metrology

standard deviation for 12 weeks dynamic repeatability test:  $\sigma$  = 9 nm (0.17 %)

## Conclusion

- FRT is a leader in surface metrology solutions for Advanced Packaging applications

- We provide the lowest cost of measurements for new heterogenous integration manufacturing processes.

- Our SurfaceSens<sup>TM</sup> multi sensor technology provides a very flexible system serving R&D as well as high throughput fully automated measurement for production.

- FRT today covers the advanced packaging industry with 40 to 90um pitch in main stream manufacturing.

- Together with leading customers we are developing next generation 20um pitch and below.

# THANK YOU

FRT GmbH

Friedrich-Ebert-Strasse 75

51429 Bergisch Gladbach

Germany