# Next Generation, Fine Pitch HBM Cube Characterization to Production

November 17, 2020

**Quay Nhin**

## Agenda

- Follow up on last year HBM paper- probing complexity and challenges

- HBM test insertions- cost and coverage

- Vertical solution status on direct access µ-bump probing

- Call to action for upcoming next generation HBM3/HBMnext

# How Does Advanced Packaging (HBM) Impact Test? **Complexity!**

| FFI Product<br>Platform |

|-------------------------|

|                         |

|                         |

|                         |

|                         |

|                         |

| Matrix                  |

| Matrix, PH              |

| Matrix, PH              |

|                         |

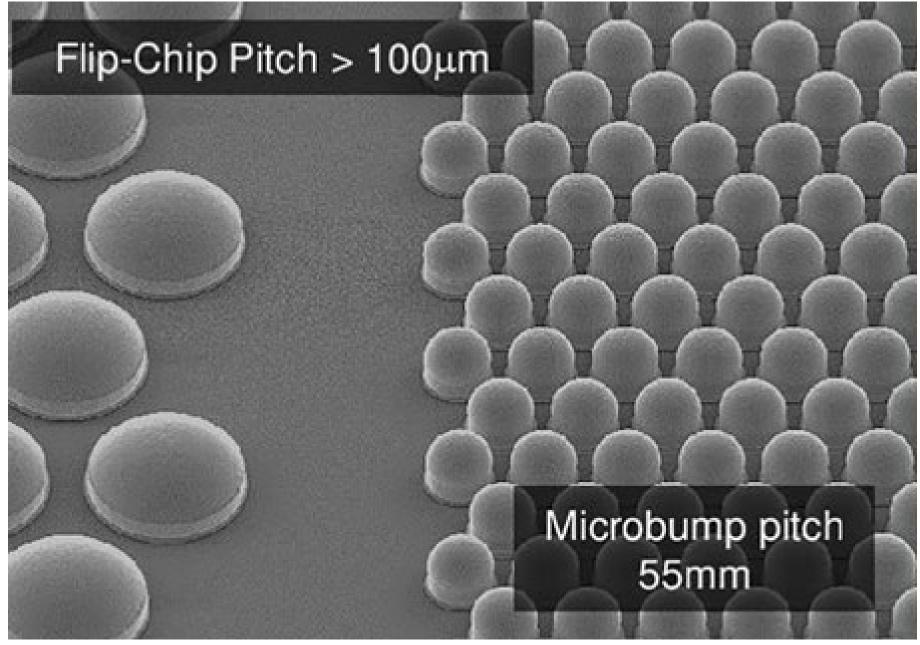

Spatial/Mechanical – Higher Density

- Smaller pitches and higher probe counts

- More delicate contacts (new materials)

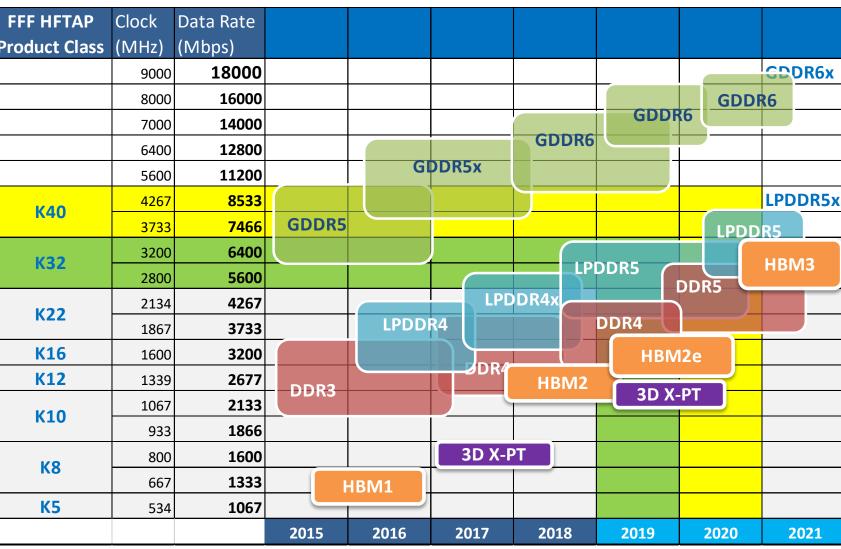

Electrical – Higher Performance Higher clock speeds, nearing RF frequencies ulletIncreased current per contact, higher power density  $\bullet$

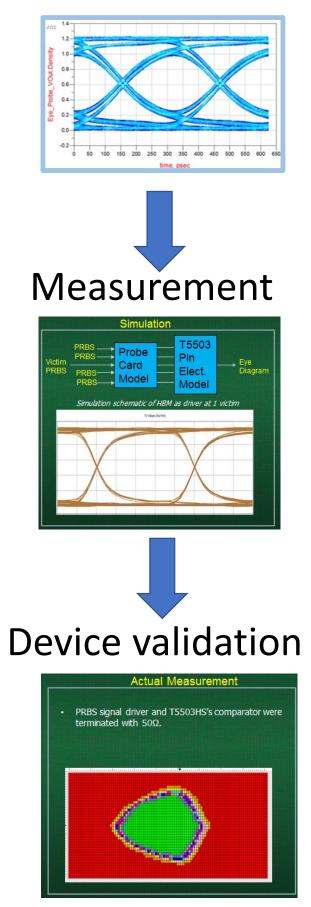

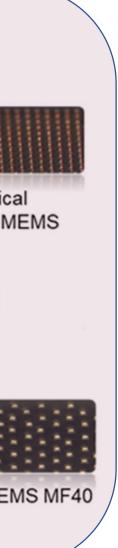

#### ATE Tester + Probe Card + Wafer = Data Eye

#### Simulation

## How Does Advanced Packaging Impact Test? **Cost, Complexity, and Coverage!**

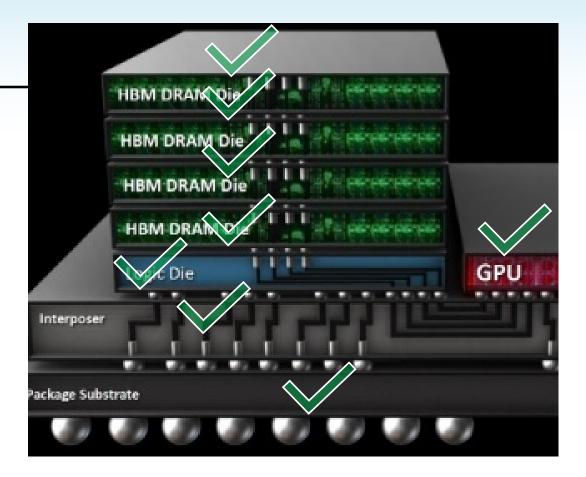

- Final test of assembled package is necessary, but provides limited insight to improve performance and yield

- Wafer test provides valuable yield learning on component die and ensures the final stacked assembly does not get scrapped because of one bad die

### Ideally, each component is good before integration

Nirvana is Known Good Die (KGD), just test everything

### **Economics may dictate something shy of KGD**

- Pre-package wafer test is fundamentally scrap-cost avoidance

- Final-test and system-test opportunities prevent escapes

#### **Cost vs. coverage optimization comes down to math**

- Compromise = Probably Good Die (PGD)

- Hedge bets e.g., design interposers/ bridges with redundant vias, and build repairability into each HBM sub-die

- Balance test coverage to catch higher-probability/impact issues, while accepting risk of lesser issues slipping through to final test

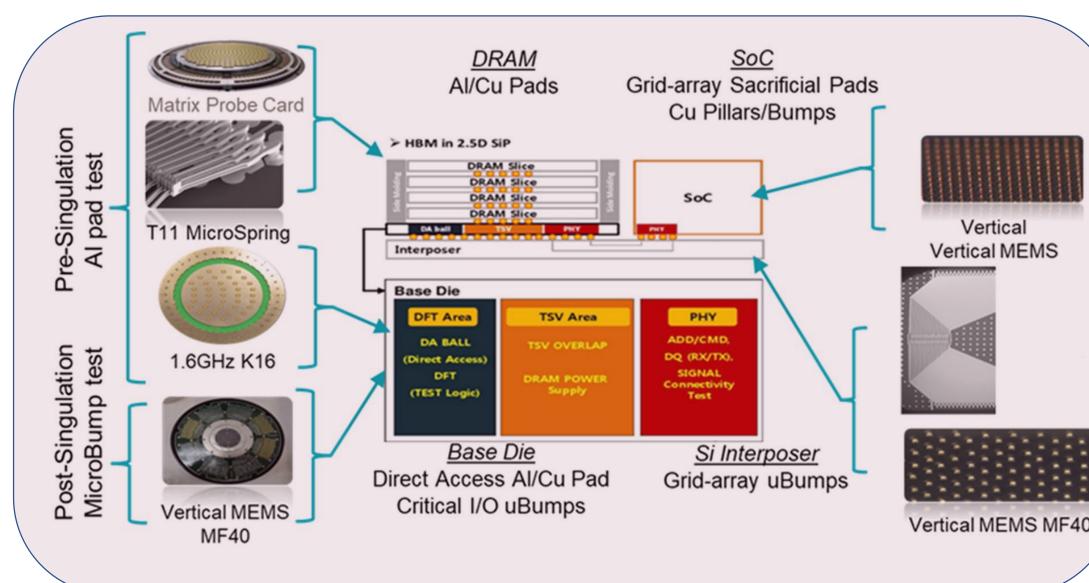

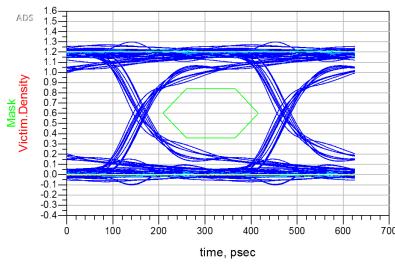

## HBM Probing Solution Status for Pad and Direct Access µ-bump

| HBM Probe<br>Solution                                                                                                                                             | DUT Config | PC pin count | <b>Operating Frequency</b> | Status     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------------------|------------|

| Vertical                                                                                                                                                          | x4         | ~15,000      | 1.6GHz/3.2Gbps             | Qualified! |

| (μ-bump)                                                                                                                                                          | x1         | ~5,350       | 1.6GHz/3.2Gbps             | Qualified! |

| Sacrificial pad                                                                                                                                                   | up to x64  | ~20,000      | 3.2GHz/6.4Gbps             | Qualified! |

| ADS 1.6<br>1.5<br>1.4<br>1.2<br>1.1<br>1.2<br>1.1<br>1.2<br>1.1<br>0.0<br>0.8<br>0.7<br>0.6<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5 |            |              |                            |            |

PCB and MLO design and manufacturing supports up to 1.6GHz and 3.2GHz

# **Next Gen HBM3/HBMnext in Feasibility Study**

## • HBM3/HBMnext on the horizon and JEDEC is firming up on the final specification

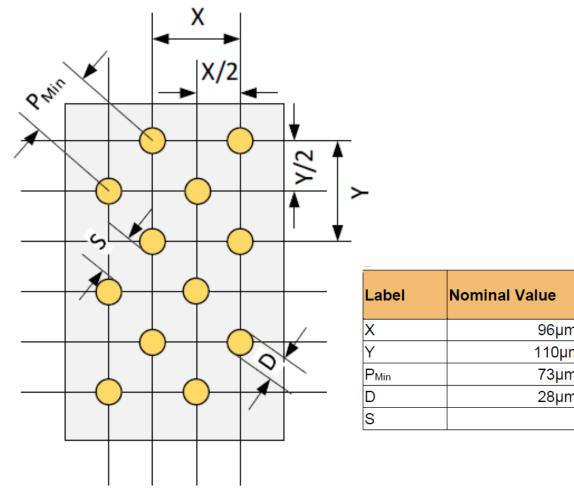

- 73um minimum stagger μ-bump pitch

- Testing of live HBM cube up to 8Gbps (4GHz)

- Sacrificial pad testing of high parallelism mass production sort up to 8Gbps at wafer-level

- Multi-suppliers and customer collaboration needed to ensure success

|   | Description                                    |

|---|------------------------------------------------|

| n | Horizontal pitch of two adjacent micro bumps   |

| m | Vertical pitch of two adjacent micro bumps     |

| n | Minimum pitch of the bump field                |

| n | Micro bump Pillar Diameter                     |

|   | Bump to Bump air gap; S = P <sub>Min</sub> - D |

THANK YOU